AI-Oneチップおよび評価プラットフォーム

[2022/3/25 第33回フォーラム発表内容]

[2021/5/28 第23回フォーラム発表内容]

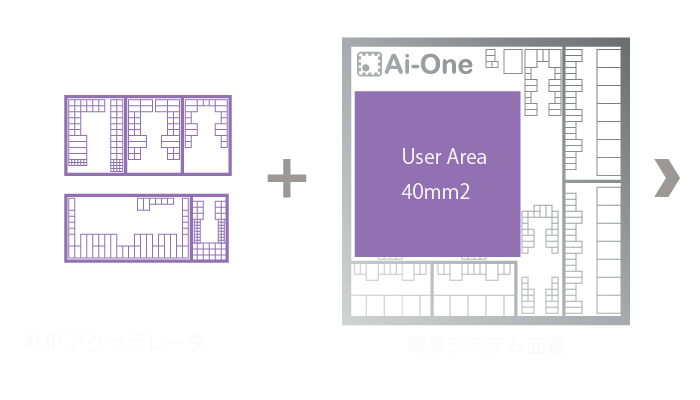

本AIチップ設計拠点では、中小・ベンチャー企業などが開発した独自アルゴリズムを実行するAIアクセラレータ向けに、評価プラットフォームの構築を進めています。 AIアクセラレータを実環境で評価するには、そのAIアクセラレータと標準システム回路を組合せたSoC、いわゆるAIチップを開発し、システムレベルの評価を行う必要があります。

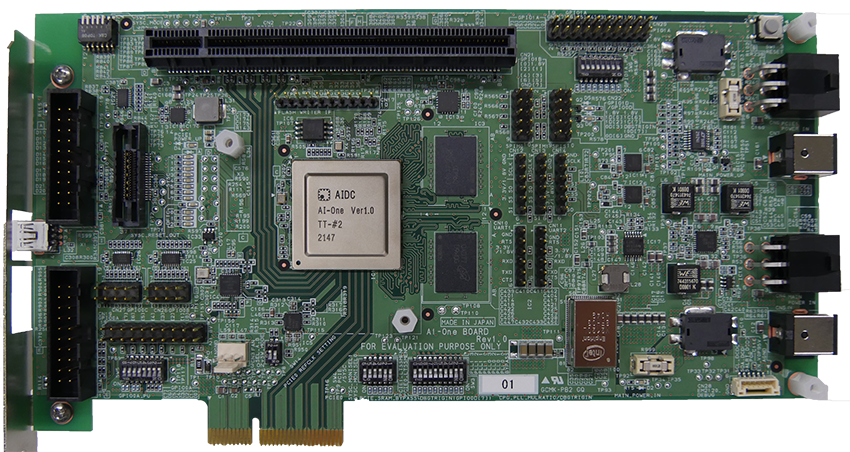

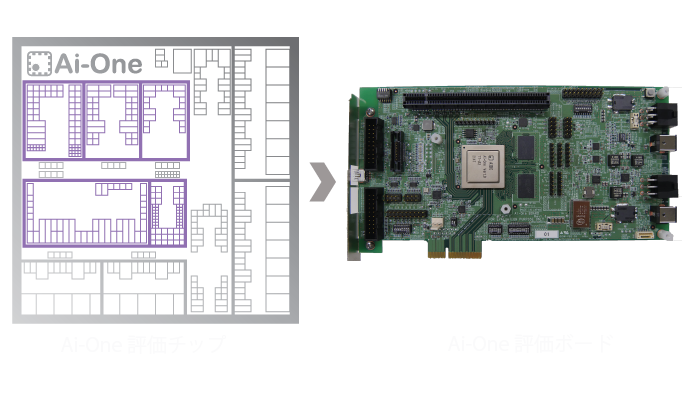

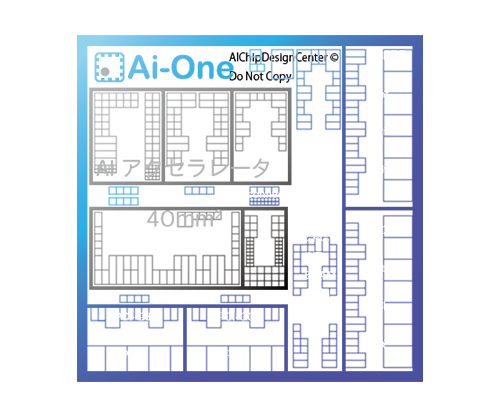

このたび、本評価プラットフォームの実証として中小・ベンチャー企業の協力を得て、6種類の独自AIアクセラレータを搭載したCMOS28nmプロセスを用いる評価チップ(AI-One)の設計を完了し、外部の製造会社にて試作したチップを搭載した評価ボードで評価を開始しました。 設計値(動作周波数、消費電力、機能、システム性能)と、実チップを比較評価することで評価プラットフォームの有効性を確認していきます。

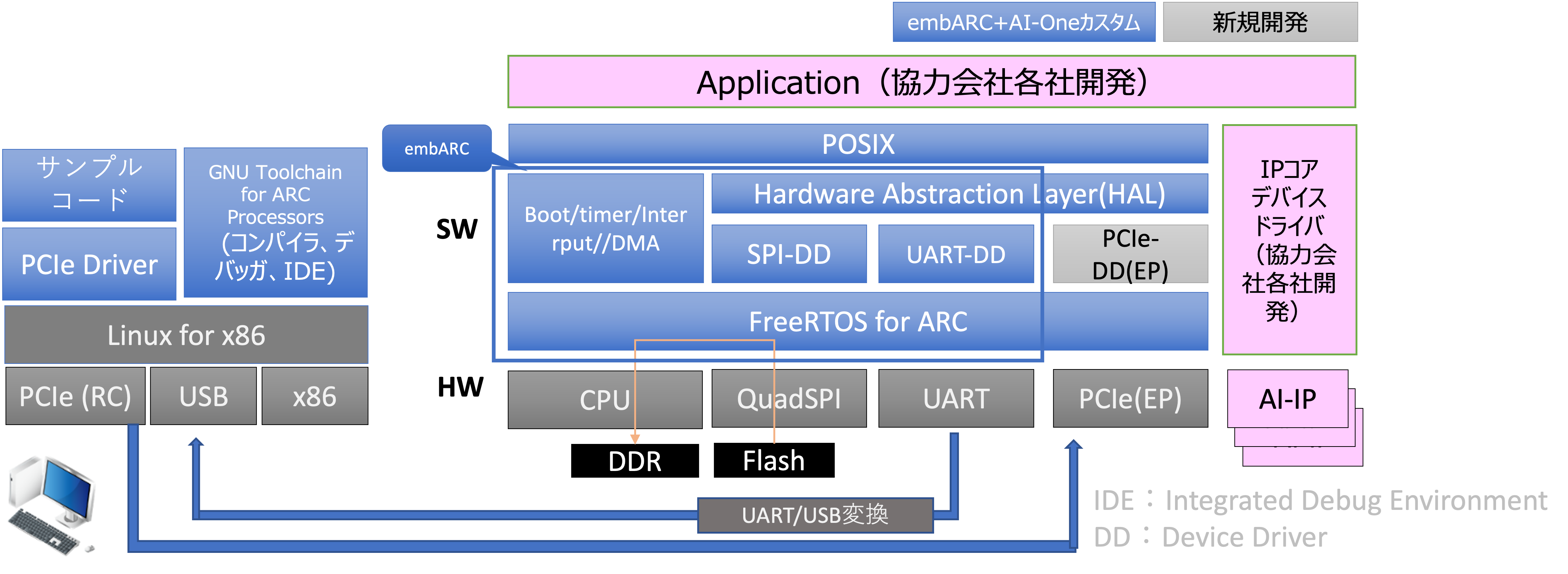

評価プラットフォーム

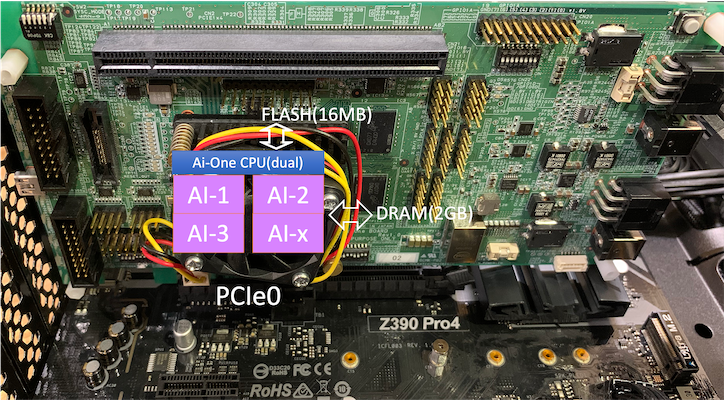

RTLガイドラインに準拠して設計したAIアクセラレータと、LPDDR4やPCIeG3とチップを制御するCPUを搭載した標準システム回路を組合わせ、拠点で整備中のEDAツール、設計ツールチェイン、設計フローを用いてAi-One評価チップを試作し、デバッカやホストPCに接続する評価ボード設計までを統合化した評価プラットフォームを開発しています。

1. 開発方法

AIアクセラレータ協力会社との開発の進め方

AIアクセラレータをご提供いただく協力会社様には、下記の設計作業をお願いします。個別RTL

・ マイルストーン、概略日程、設計データのリリース要件の説明 ・ 各マイルストーンまでに実施する項目の説明 ・ RTLガイドラインの説明 ・ SpyGlass、DesignCompiler、FormalityによるIPの設計データ検証方法の説明 ・ NOCインターフェイス仕様の提出 ・ Iolistによるインターフェイス情報仕様の提出 ・ SRAM要求仕様書の提出 ・ 合成可能RTLの提出

RTL Pon (RTL Power on)

・ 1ChipSimulation 環境の提供 ・ SRAM生成用コンフィギュレーションデータ収集と物量の把握 ・ 物理インプリメンテーションの初期実行結果の説明とAIアクセラレータへのフィードバック

DF ( Dirty Final )

・ CF向け論理検証項目の説明と依頼 ・ 物理インプリメンテーションからAIアクセラレータへのフィードバック ・ 拠点での各種検証結果のフィードバック

CF ( Clean Final )

・ ポストCF論理検証項目の説明と依頼 ・ タイミング検証結果確認項目の説明、依頼 ・ 論理変更用ECOフローの説明

ECOファイナル

・ サインオフ検証項目の説明と依頼 ・ 論理変更用ECOフロー用等価検証環境の提供 ・ 論理ECOの提出(注釈)

・ NOC: Network On Chip (チップ内ネットワーク)

・ AIアクセラレータ協力会社:開発中の評価プラットフォームの有効性を確認するためAIアクセラレータを提供いただき、評価プラットフォームと評価チップ(Ai-One)の開発に協力いただいている。

各AIアクセラレータ仕様に合わせた変更箇所と搭載したテスト機能

各アクセラレータとの接続にカスタマイズが必要な標準システム回路 ・ SYSC (リセット、モード信号、各IPの動作制御レジスタ) ・ NOC (データをリードライトするチップ内オンチップネットワーク) ・ 割込み制御 ・ デバッグインターフェイス

オンチップテスト機能として標準装備したテスト機能 ・ Logic BIST テスト (標準ロジック製造テスト) ・ Memory BIST テスト (内蔵メモリ製造テスト) ・ PLL テスト (高速クロック生成テスト 再利用可) ・ PCIe PHYテスト (高速シリアル転送テスト 再利用可) ・ LPDDR4 PHYテスト (高速パラレル転送テスト 再利用可)

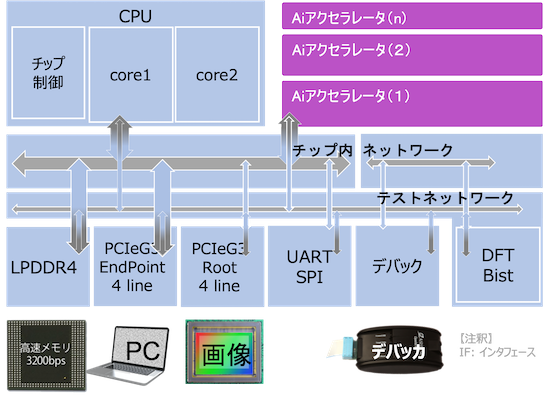

2. 標準システム回路

標準システム回路とは、PCIeやLPDDR等の高速IO回路、チップを制御するCPU回路、検証回路、テスト回路、および評価ボードなどの共通基盤技術で構成されます。この共通基盤技術をAIアクセラレータ向けに統合化した設計環境が評価プラットフォームとなります。

・ CPU:デュアルコア構成でシステムレベルの評価に必要なRTOS、LinuxなどのOSやAIアクセラレータ向け前処理・後処理プログラムを実行。 ・ チップ内ネットワーク:AIアクセラレータのさまざまなインタフェース要求に対して、チップ内のネットワーク機能を提供。 ・ LPDDR4:低消費電力DDR(Double Data Rate)型ダイナミックメモリをチップに接続するための高速メモリインタフェース回路。 ・ PCIeG3 EndPoint/Root:PCなどの標準的な周辺インタフェースであるPCI Express 3.0に接続するための回路。 ・ UART、SPI:チップのデバッグ機能やプログラムを読み込むFlashメモリインタフェース、シリアルインタフェイス、パラレルインタフェイスなど。 ・ DFT、Bist:チップ内部の論理回路や内蔵メモリの故障検出機能を提供。

3. 設計Flow

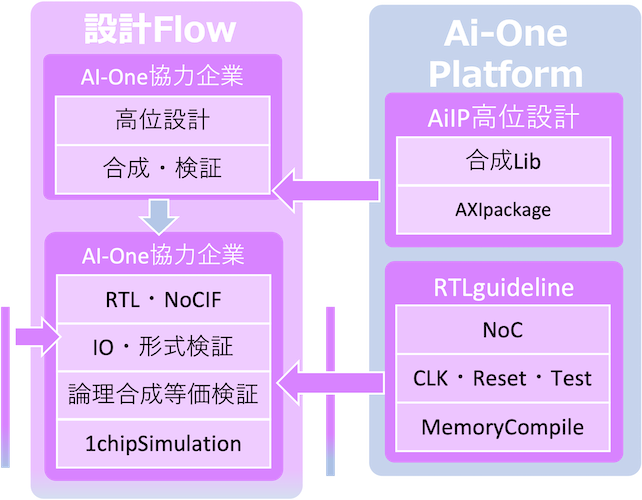

下図に設計Flow(*)とAi−OnePlatform(*)の構成要素と設計内容を示します。

(*)設計Flowとは、EDAツールを使用してブロックやチップ設計を行う作業工程です。

(*)Ai-OnePlatFormには、拠点で整備した設計環境やCompileしたIP-Libertyが含まれています。

設計Flow Ai−OnePlatform

設計内容

Aiアクセラレータ搭載

AIアクセラレータがC++の場合は、以下のツールをご使用ください。 ・設計ツール:Catapult ・合成・検証:Catapult Xilinxで開発したC++はCatapultで検証ねがいます。 ・拠点が提供する合成Lib・AXIpackageを使用してください。 Xilinxの実行ライブラリモデル(RTL)は契約上使用不可です。 ・CatapultでRTLを生成します。 AIアクセラレータのRTLが出来たら、 ・AXIインタフェース仕様を提出願います。 ・Clock、Reset、DFTのprimitive modelをInstanceしてください。 ・使用するMemoryのサイズを提出ねがいます。 ・iocheck:TopModuleのIOポートをとIOList(Excel)を検査します。 ・Spyglass:形式検証でRTLの構文がLSI化できるか検査します。 ・DesignCompiler:物理Libertyを使用して論理合成し、動作周波数を検証します。 ・Formality:等価検証でRTLと合成結果の論理が同一である検証を行います。

設計Flow Ai−OnePlatform

設計内容

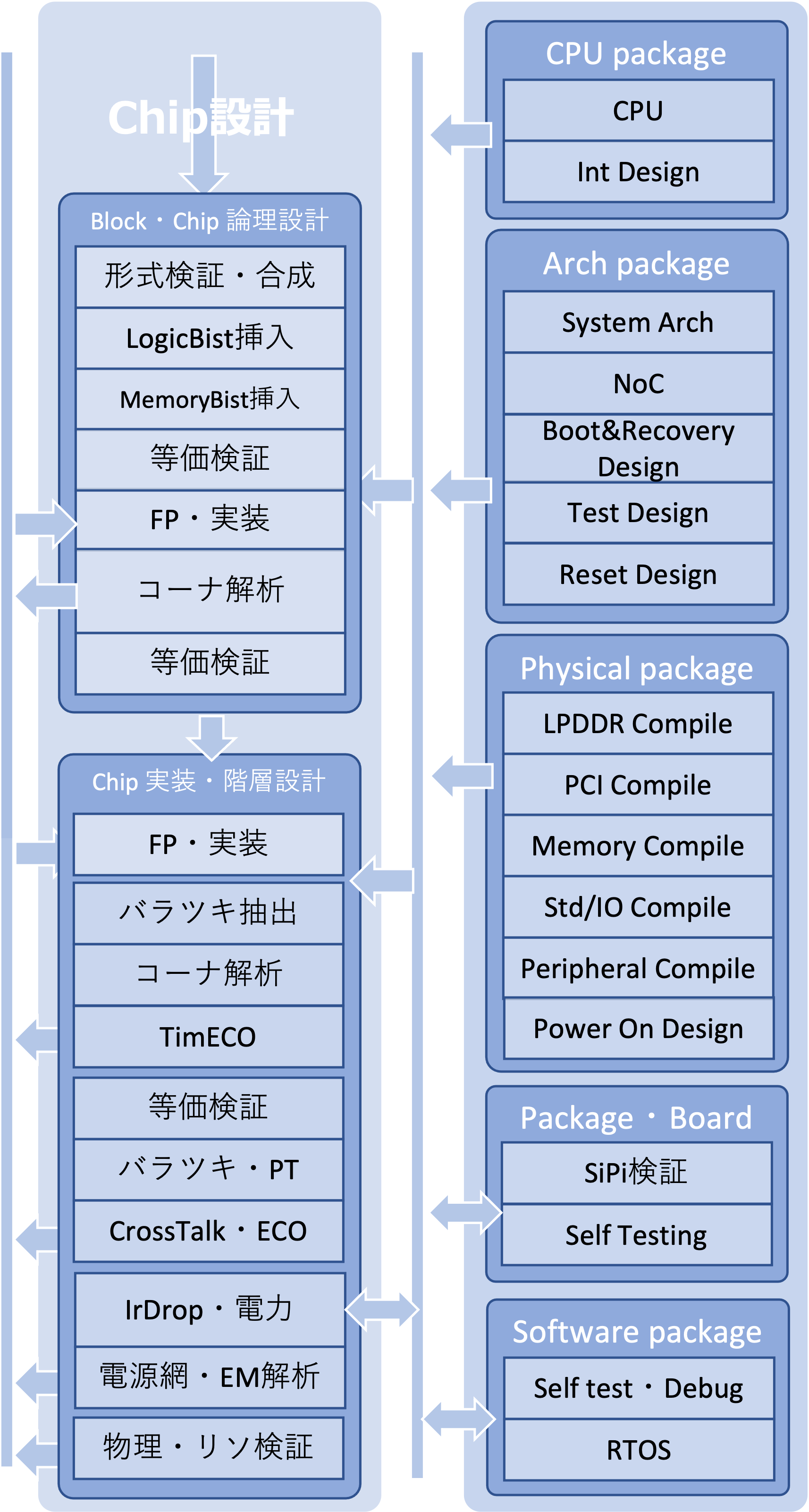

評価チップ設計

Block論理設計 ・形式検証・合成では、全てのModuleの形式検証と論理合成を行います。 ・LogicBist挿入、MemoryBist挿入では、AIアクセラレータやNoC等にDFT設計を行います。 ・等価検証では、DFT結果確認のため上記の2つの工程結果について等価検証を行います。 ・FP・実装では、各ModuleのFloorplanと実装設計を行い、結果をレポートします。 ・コーナ解析では、プロセス、電源、温度、ばらつきを考慮したタイミング解析を行います。 ・実装設計を行い各ブロックのLSI化可否を検証します。 Chip実装 ・FP・実装では、ブロックをチップに組上げます。 ・バラツキ抽出とコーナ解析では、Timing検証(各コーナ、バラツキ、モード)を行います。 ・TimECOでは、TimingエラーをECOで対策します。 ・等価検証では、TimECO結果確認をおこないます。 ・バラツキ・PT、CrossTalk・ECOでより詳細なTiming検証を行います。 ・IrDrop・電力、電源網・EM解析検証を行います。 ・物理・リソ検証を行います。 CPU ・2つのHS38CPUコアをAi-One向けに生成 ・Chipの制御 ・AIアクセラレータの入出力データを前後処理 ArchetecturePlatForm

・NoCの構造、BootやRecovery制御、Test機能、Reset制御を提供します。 物理部品 ・TSMC28HPC+向けにAi-OneのArchetectureに従った物理Libertyを提供します。 Package・Board・SoftwarePlatform ・SIPI検証を実施します。 ・Debugger接続に必要なドライバーを提供します。 ・RTOS実行に必要なドライバーを提供します。

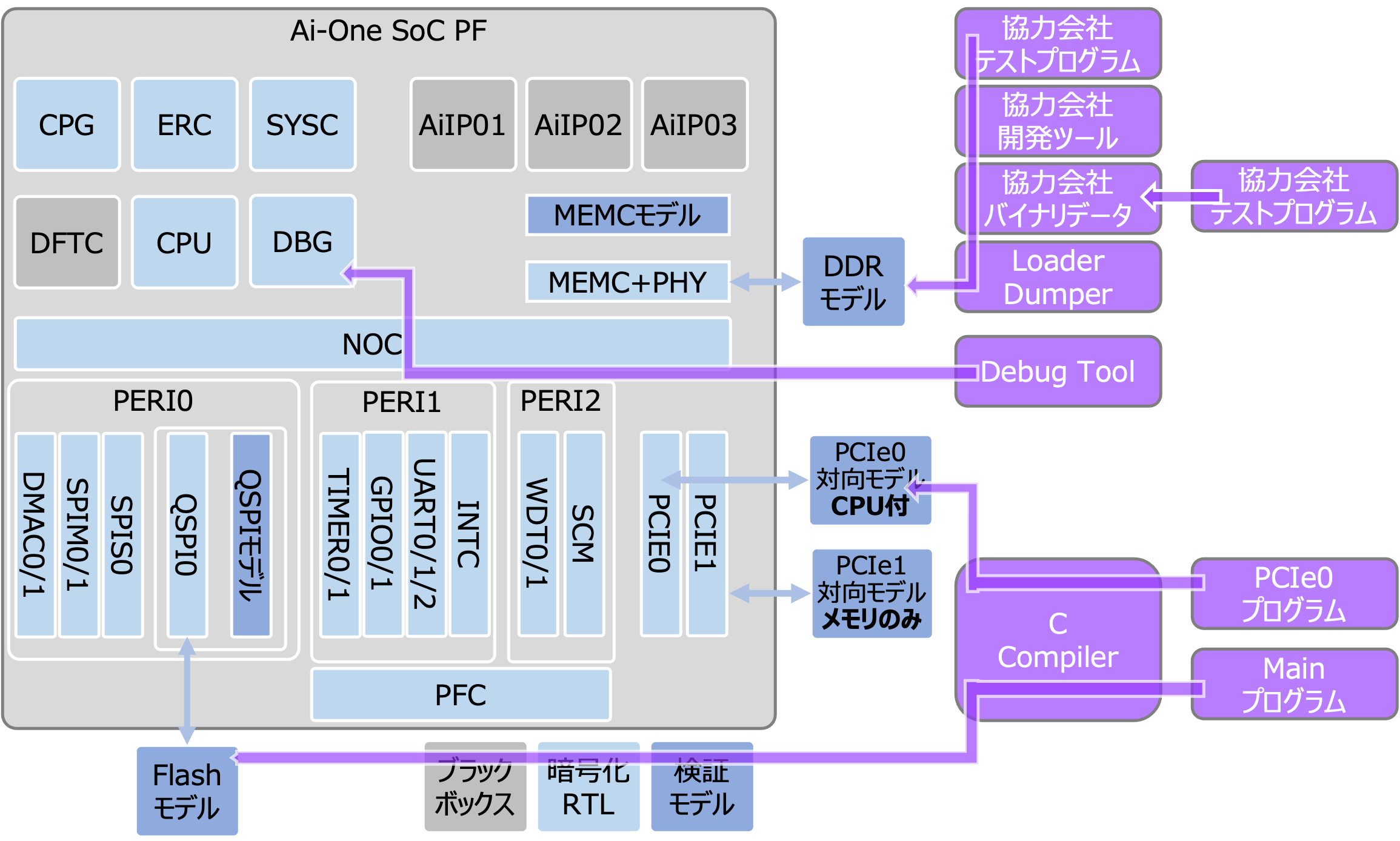

4. 1ChipSimulation

1chip 動作をRTL simulationするモデルです。AIアクセラレータをチップレベルで性能評価と検証できます。

・ Inter-ConnectにAiアクセラレータを接続します。 ・ CPUのprogramをcpu.cに記述し、Stimulasはmain_scenario.vに記述します。 ・ LPDDR4は、RTLモデル、3200bps、2400bpsモデルを選択します。 ・ PCIeは、EndPoint/RootComplexモデルがあります。対向モデルからのLoader/Dumperがあります。 ・ Meta Ware Debuggerをサポートします。

5. Feedback

チップ全体のフロアプランによってブロックの端子位置を設定でき、ブロック内のフロアプランと配置配線試行から以下のようなフィードバック情報を得ることができます。

・ タイミング違反 ・ セル占有率 ・ 配線混雑度 ・ 配線ショート これらの情報に基づき、AIアクセラレータの構造とSRAM構成、ブロック内のフロアプランとチップ全体のフロアプランを修正します。

6. パッケージとボード

チップ、パッケージ、ボード設計と並行して以下の項目をシミュレーションで確認します。

・ Sinal Integrity ・ Power Integrity ・ 熱解析

パッケージ設計 サブストレート8層

パッケージは、回路を構成するインスタンス数が少ない

自分で設計するには電気、ハードウェアの知識とツールが不可欠

Signal Integrity、Power Integrity検証

チップ、パッケージ、ボード設計と連携して

Sinal IntegrityやPower Integrity、熱解析をシミュレーションで確認

LPDDR4 Signal Integrity解析

PCB基板上の配線設計情報を基に

LPDDR4などの高速インターフェイスの信号品質をシミュレーション確認

評価基板でのSoCテスタビリティと評価サポート

ソフトウェア開発主体の会社ではLSIテスタの利用以前にLSIテスタの使用準備のハードルが高い

ボードのみである程度の評価が閉じればSoC開発のハードルが下がる

動作周波数、電源電圧の変更は評価ボードとPCで評価できる

SoC・ボード製造テスタビリティ

製造した基板のテストの簡略化がハードウェア専門家のいない会社には重要

製造テスト専門の会社に業務依頼を行うには専門の知識が要求される

標準システム回路をはじめとした共通機能のテストはパッケージ化しておくべき

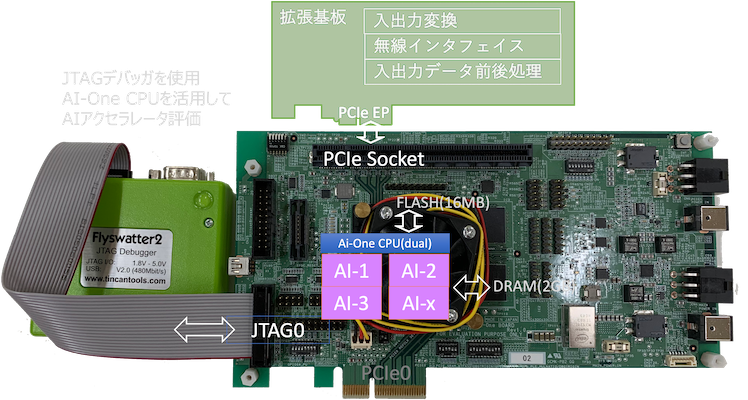

7. 評価方法

JTAGデバッガを使用して評価・デバッグする。評価の立ち上がりが早い

Linux ホストPCを介して評価・デバッグする。大量テストデータ処理が可能

Linux ホストPCからはPCIeデバイスドライバを介して制御、データ伝送が可能

Ai-Oneのすべてのリソースにアクセス可能

8. ソフトウェア

Ai-One ソフトウェアプラットフォーム(RTOS版) 開発コストの低減やユーザの拡張性、保守性確保のため embARC Open Software Platform(OSP)ベースで開発 embARCはFreeRTOSベース

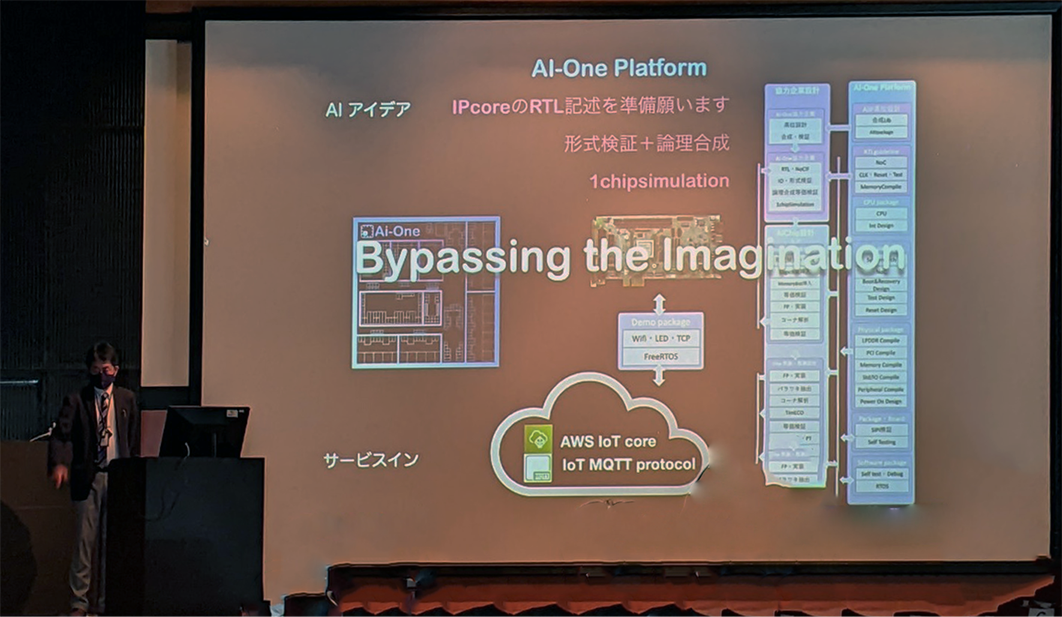

9. DemoSession

Bypassing the Imagination

Ai-One Chip is successfully Working

Thank You for Your Contributions

Built-in 6 AI Accerators

Ai-One chip signed off

2020.04 RTL

2020.07 PoN

2020.09 DF

2020.12 CF

2021.02 Tapeout

2021.12 Package ready

2022.03 33th AIDC forum

・Contributors Demos

・Ai-One Chip Platform

・Connect AWSIoT Demo

10. まとめ

エッジ向けAIチップの設計を容易にするために、AIチップに使用されるAIアクセラレータ開発のための評価プラットフォームの構築を進めています。このたび、本評価プラットフォームの実証のため、仕様が異なる6種類のAIアクセラレータを同一チップに搭載した評価チップの設計を完了し、外部の製造会社で試作を開始しました。今回設計した評価チップ(AI-One)を用いて、設計段階で見積もった各アクセラレータの消費電力、動作周波数などを、実チップを搭載したボードで比較評価を行い、アクセラレータの実環境での評価を進めます。そのフィードバックを活用してさらに使いやすいエッジ向けAIチップの評価プラットフォーム実現を図っていきます。

11. 謝辞

本評価プラットフォームの評価および評価チップの開発にあたり、以下の5社にご協力いただきました。株式会社ディジタルメディアプロフェッショナル

株式会社プリバテック

LeapMind株式会社

株式会社ロジック・リサーチ

12. 来年度プログラム

来年度プログラムの計画を検討中です。詳しくは拠点にお問合せください。13. Ai-One-Webinar

21年度拠点フォーラムで紹介しました内容は、Information/e-講座・Webinarに掲載しています。

AIチップ設計拠点 Confidential Document