半導体設計セミナー

LSI設計を俯瞰できる技術者を目指します。

LSI設計に必要な計算機利用技術

Linux、Shellプログラミング

LSF、Licensing、EDAマニュアル

拠点はじめてLogin

NoMachineのInstallと設定

Desktop設定

Linux設定

Directory構造

RefreshLinux

環境ファイルとは

タイムスタンプの重要性

環境の複写とcopyの違い

Shellプログラム

実行とStatus

パイプとコマンド

正規表現の利用

EDAツール実行

LSFとは

実行環境作成

実行と結果の確認

条件を変更する

複数の実行とその順

LicenseとCPU

複数の結果比較

問題点の発見と対策

結果の確認

Shellコマンド

ErrorとWarning

問題点の発見

マニュアルの検索

対策と再実行

RTLガイドラインを利用

SpyGlass、Xcelium

DesignCompiler、Formarity

形式検証

Spyglass環境設定

Directory構造

AiIP0X.f作成

実行とエラー解析

対策と再実行

1ChipSimulation

Xceliume環境設定

Directory構造

cpu.cとmainsenario.v

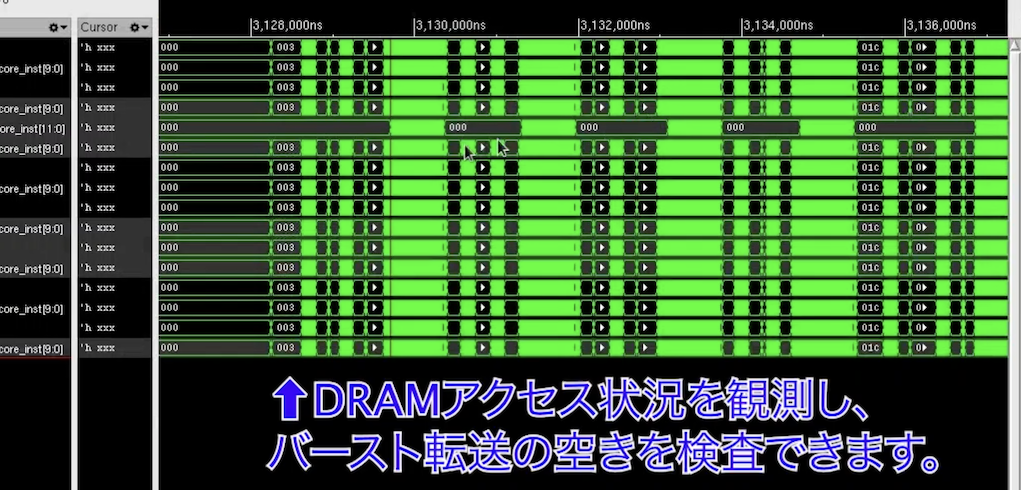

波形の観測

LPDDR4モデルと評価

PCIeホストエンドポイント

SPIからプログラムBoot

論理合成・等価検証

DesignCompiler環境設定

Formality環境設定

Directory構造

実行と結果の確認

条件を変更する

複数の実行

LicenseとCPU

複数の結果比較

HVT・SVT・LVT

期待と実際

実行条件設定

複数の実行

結果の纏め

自動配置配線

ICC2、PrimeTime

DesignCompiler-topo、DesignVision

Module実装

ICC2環境設定

Directory構造

SRAM配置

実行とエラー解析

対策と再実行

SRAM配置

DEF構造

考慮すべき点

Scriptの作成

デバックと対策

Feedback

StaticTiming解析

PrimeTime環境設定

Directory構造

実行と結果の確認

LicenseとCPU

合成可視化

DesignVisionの概要

環境設定

Directory構造

実行

物理検証

Calibre, Virtuoso, CustomCompiler

ModuleDRC

マニュアルの見方

Calibre環境設定

ダミー生成とDRC実行

Virtuoso環境設定

エラー解析

SRAM配置対策

DEF構造

考慮すべき点

Scriptの作成

デバックと対策

Feedback

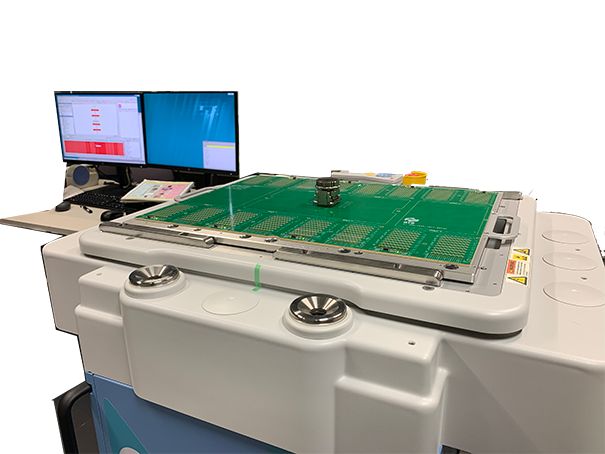

チップのデバックとは

評価ボードとテスター

評価ボード

ホストPC設定

JTAG設定

起動とデバック

エラー解析

Core電圧評価

テスター解析

(TBD)

テスター起動と接続検証

テストパターン作成

デバックと対策

Simulationとテスタの違い

LSI設計時に発生する問題点を自力で発見し

解決策を実施し結果を評価できる

LSI設計エンジニアを目指します。

(Onsiteインターンシップを実施し、カリキュラムの有効性を評価中)

AIチップ設計拠点 Confidential Document