EDAツール

350種類のFeatureと262種類のツールバージョン

Ai-One・Ai-Twoの動作確認バージョンを公開

FabのPDKに準拠したツールとバージョン

262種類のツールバージョン

/.../<vendor>/env

|--/apps/.../<vendor>/.../cshrc…Q-2019.12-SP2

|--/apps/.../<vendor>/.../cshrc…Q-2019.12-SP3

:

動作確認したツール組合せを公開

Ai-One

/apps/.../<vendor>/.../cshrc…20.09.001

/apps/.../<vendor>/.../cshrc…R-2020.09-SP5-2

:

Emulator

ASIC based Emulator

Emulation Capacity 2,304MGate

72 Boards・576 Domains

UMC(User Memory Card) 4,608GByte

DDC(Data Capture Card) 4,608GByte

論理検証・システム検証・性能消費電力

VIP

Ai-TwoではLinuxBootをEmulatorで実施しました。

IPcore

汎用製品に搭載された実績のあるIPcore

Ai-One, Ai-Twoチップで動作確認ずみConfiguration

ロジックBist、メモリBist救済を実施

MCUforRTOS

SingleCoreCPU

DSP・FPU

USB・MIPI・I2C・UART・SPI

ADC/DAC・StdCell・SRAM

CPUforLinux

Dual Core

DMAC・DBG・InterConnect

SDMI・I2C・UART・SPI・GPIO

LPDDR4・PCIeG2・USB・MIPI

ADC/DAC・StdCell・SRAM・ROM

PDK・PLL・SMS・SHS

HighEnd

Dual Core

DMAC・DBG・InterConnect

SDMI・I2C・UART・SPI・GPIO

StdCell・SRAM・SMS・SHS

LPDDR4・PCIeG3

PDK・PLL

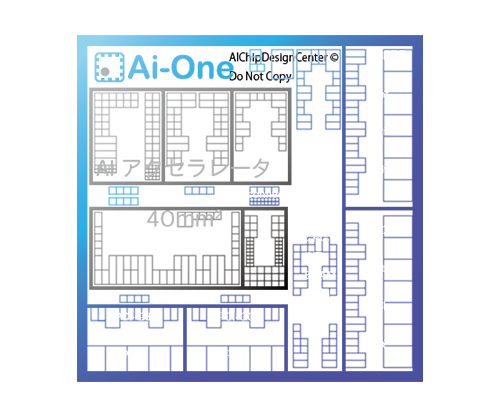

Platform

AIアクセラレータをInterConnectで接続

SoC標準回路は、LPDDR・PCIe・CPUや

INT・DMAC・DBG・BIST・UART・SPI

Fabに準拠した設計ツール・IPを設定

半導体会社でLSI設計経験があり新たなスタートアップ企業で、半導体会社同等のプラットフォームを利用

LPDDR4やPCIeG3のConfigurationを参照

ネットワークインターフェイスのConfigurationを参照

LogicBist, MemoryBist, debug方式を参照

1chipSimulation

AI read/write DRAM

AI read/write CMEM

performance check

CPU read/write AI-Reg

PCIe read/write AI-Reg

Int and recovery

Check frequency

Reset and start

Start from QSPI

RTLguideline

InterConnect接続仕様と検証

ResetとClock設計と仕様

RTL形式検証とsgdc・swl設定

RTL形式検証の評価

論理合成と合成条件

論理合成の評価

実装設計からのFeedback(option)

Ai-OneProgram

Platform開発にご協力いただく企業を募集

協力企業は以下の項目を日程に従い実施

AiIPを提供しPlatformに組込

RTLガイドラインに準拠

1chipSimulationを実施

実装結果のFeedbackに対処

評価チップの検証

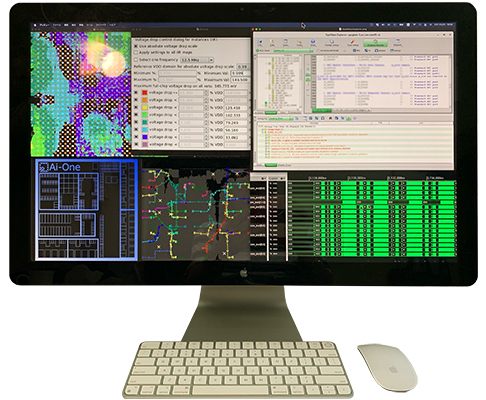

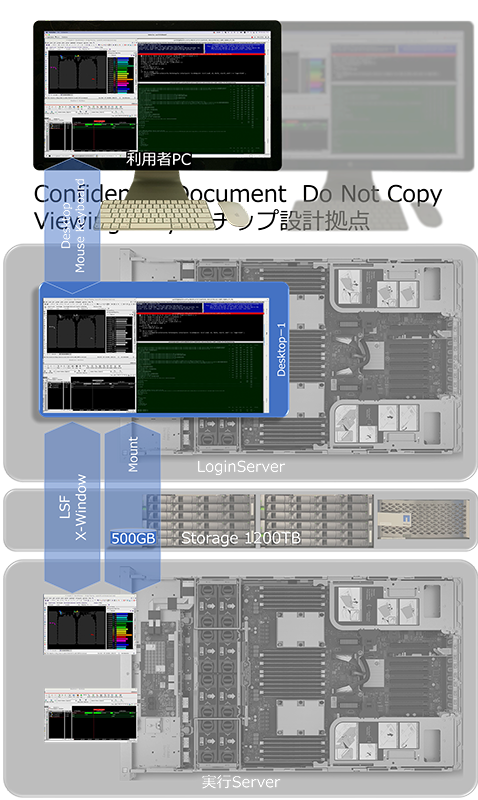

EWS

LSI設計ワークロードに特化したベアメタルインスタンスを提供

繁忙期にはサーバリソースや利用者を追加

利用者PCでCloud接続

利用者PCで拠点Cloudに接続し設計

利用者PCに専用ソフトをインストール

専用ソフトはWindows, MacOS, Linuxをサポート

利用者PC画面にLoginServerの設計用Desktopを表示

Keyboard・Mouseで遠隔操作

回線切断発生でも再接続で、Desktopは中断しません

・

LoginServer

設計用Desktopを起動し、

Terminalで論理設計やジョブを準備

専用Linuxを利用Project毎に導入

LSFで実行Serverにジョブ投入

Loginするユーザを追加可能

2つのServer構成種類から利用目的で選択

・専用Linux LoginServer(標準)

・ベアメタル LoginServer(高速)

Storage

設計用Volumeは500GBで、200GB単で追加

LoginServerと実行ServerにMount

実行Server

設計ツールを起動

LSFでLoginServerからジョブ受付

4つのServer構成種類から利用目的で選択

・共有実行Server(スタンダード)

・専用実行Server(PDK・IP使用)

・エミュレータ実行Server(エミュレータ)

・ベアメタルServer(大規模設計)

・

・

Fab連携

国内外Fab連携

現在は国外Fab1社と2つのプロセスのPDKで連携しています。

PDKとプロセスに準拠し、設計ツールのパラメータを設定する必要があります。

拠点では、設計ツールのパラメータ設定が動作することをチップで実証ずみです。

この動作確認済みの設計ツールの設定は、Platformを参照することで閲覧できます。

拠点利用者は、拠点が連携しているFabとの契約があれば連携が可能です。

複数FabのPDKを使用した同時設計は、事前にFabへの確認・承認をお願い致します。

国外FabとIPcore連携

IPcoreは利用目的に従い仕様(Configurationという)を決定する必要があります。

例えばLPDDR4の仕様決定には、LPDDR4の専門知識とSoCシステムの要件抽出が必要です。

拠点では、このConfigurationの組合せが動作することをチップで実証ずみです。

この動作確認済みのConfigurationは、Platformを参照することで閲覧できます。

利用には、CAA*1, EULA*2等の契約が必要です。

*1 Core Access Agreement

*2 End User License Agreement

リファレンスデザイン

AIチップの開発においては、AIコアIPを慎重に設計・検証することはもちろんのこと、目的に合ったメモリIPやバスインターフェイスIP等といった周辺IPを適切に選択し、AIコアIPに組み合わせることでAIチップ全体を完成させていいきます。

このような設計・開発は豊富な技術的知見や経験を必要とします。また、設計ツールやIPを用いた設計フローを組み合わせて実際のチップを設計する場合、様々な利用方法に関するノウハウが必要です。

AIチップ設計拠点では、革新的なAIソフトウェア技術を持った中小・ベンチャー企業の研究開発を支援するために、リファレンスデザインを研究開発し、チップ開発のノウハウを持たない方々のチップ作製を支援します。

TCAD

Impulse TCADは半導体デバイスの特性を把握するためのデバイスシミュレータです。

産総研が独自開発しているので、本拠点に相談いただければ様々な物理モデルやパラメータに対応させることができます。

Impulse TCADの特徴: 自動微分の採用により、新規物理モデルの組込が容易 分散並列処理により、大規模解析が可能 センサーなど独自デバイスに対応可能

研究開発内容: ユーザーインターフェースの開発 CMOSイメージセンサーなど半導体デバイスのデバイスシミュレーション

AIチップ設計拠点 Confidential Document