a2024/04/26【Webフォーラム開催】AIチップ設計拠点フォーラム(第58回)

1. 日時:4月26日(金) 13:30 - 16:40

2. 開催方法:Webフォーラム (3月23日までの参加申し込みが必要となります)a2024/04/25202404論理エミュレータセミナー

1.日時:4月25日(木)13:00-15:30

2.開催方法:現地講習会形式 (東大 武田先端知ビル1F)

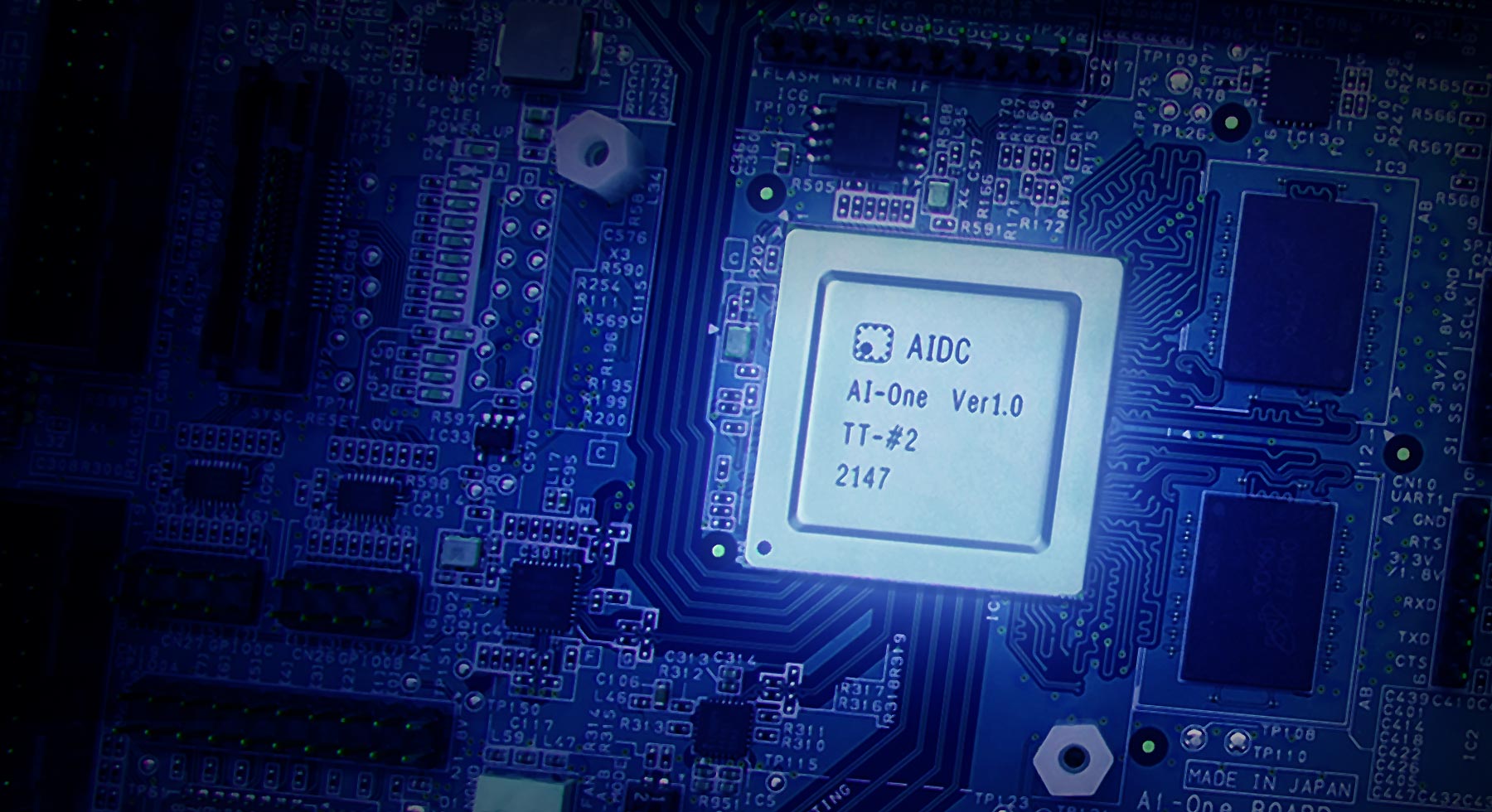

AIチップ設計拠点とは

国立研究開発法人 産業技術総合研究所【理事長 石村 和彦】(以下「産総研」という)エレクトロニクス・製造領域【領域長 安田 哲二】と国立大学法人 東京大学(以下「東京大学」という)【総長 藤井 輝夫】大学院工学系研究科附属システム デザイン研究センター基盤設計研究部門は協力してわが国の革新的なAIチップ開発を加速するための「AIチップ設計拠点 AI Chip Design Center (AIDC)」を、東京大学 本郷地区キャンパスに構築しました。

本拠点の半導体設計環境は、NEDO委託事業(*1)により整備され2019年10月7日から試験運用を開始し、2023年04月01日より産総研TIAの共用施設(*2)として本格稼働し、国内半導体の自社研究開発向けに半導体設計設備を提供しています。

拠点利用者は、利用登録を行うことにより、外部からのリモート接続や、設計ブース(本拠点内)の利用によって、半導体設計環境を利用することができます。 また、本委託事業で開発したAIチップ開発のための共通基盤技術やAIチップ設計技術者育成のための教育カリキュラムの提供も行っています。

*1 「AIチップ開発加速のためのイノベーション推進事業/【研究開発項目②】AIチップ開発を加速する共通基盤技術の開発」

*2 産総研TIA共用施設